2023-11-21 11:59:40 凤凰网财经

本月初,硅谷科技巨头谷歌宣布,安卓系统正式支持 RISC-V 架构,在其官方博客中写道:“Android 支持许多不同的设备类型和 CPU 架构,我们很高兴在列表中添加一个新的架构 —— RISC-V。”

在过去的几十年中,英特尔和 Arm 在 CPU 架构领域一直保持着领先的地位。然而,RISC-V 加入到安卓生态系统无疑对此构成了有力的冲击。作为全球数十亿智能手机和可穿戴设备市场的领导者之一,谷歌对 RISC-V 的支持预示着行业的重大转变。

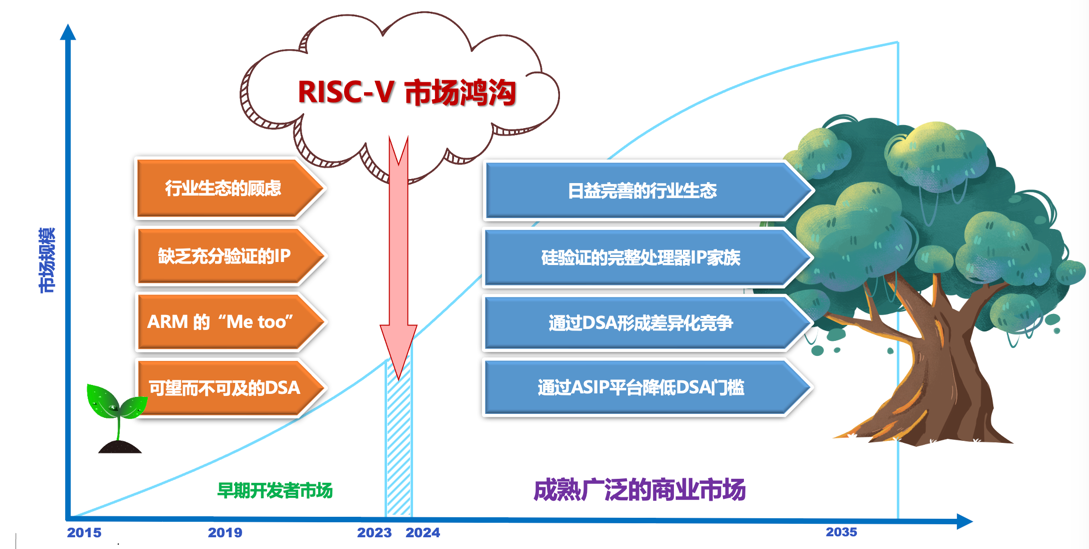

“三位一体”的解决方案,推动RISC-V跨越市场鸿沟走向成熟商业市场

随着国际大厂和国内造芯新势力的不断加入,RISC-V 生态正在全球范围内蓬勃发展。但是,RISC-V 从实验室开发研究走向成熟商业应用的过程中,还面着临充满挑战的市场鸿沟。

由于 RISC-V 的开源性质,前期部分上市企业的 RISC-V IP 缺乏充分的硅验证,导致在芯片真正投产时出现各类质量问题,极大影响了客户使用 RISC-V 进行芯片量产的信心。此外,早期 RISC-V 芯片企业倾向采用对标 ARM 产品的模式,推出的处理器 IP 成了 ARM 的“平替”。这种模式除了价格低廉之外缺乏真正的竞争力。

而实际上,RISC-V 的核心优势在于它的可定制性,通过 DSA 方法论,可以构建具有差异化竞争力的处理器架构,实现 ARM 授权模式无法给予的灵活性,自主性和市场竞争力,从而为客户提供不可替代的全新价值。

目前,DSA 方法论的重要性和优势已被行业广泛认可,但要实现这种方法论,需要有经验丰富的团队,并投入大量的人力和时间进行研发,摆在行业面前的仍然是一道无法轻易逾越的鸿沟。

凭借商用 IP 核+ASIP 设计平台+专家服务,隼瞻科技向市场推出了“三位一体”的 RISC-V 解决方案,扫清了硬件、软件和服务生态等各方面的障碍,为 RISC-V 走向成熟市场铺平道路。

硬件方面,隼瞻科技基于 RISC-V 架构,研发了覆盖 MCU、实时 CPU ,DSP到高性能多核CPU 等一系列处理器 IP。每一款 RISC-V 处理器 IP,都经过严格的系统验证,再通过投片进行硅验证(Silicon Proven),以确保其可用性和硅效能满足商用级别的要求。

软件方面,隼瞻科技向芯片企业提供了 ASIP 敏捷开发 EDA 平台 Wing-Studio,使芯片设计人员可以专注于架构和指令集设计,摆脱RTL级别的繁复开发工作。

与此同时,隼瞻科技还配备了芯片定制设计服务专业团队,协助客户进行前期的需求分析规划、系统分析、架构探索,助力客户设计出在其垂直领域具备显著优势的处理器子系统,令客户的最终 SOC 芯片产品具备强大的市场竞争力。

可以预期,随着隼瞻科技“三位一体” RISC-V 解决方案推向市场,阻碍 RISC-V 生态系统走向商用成熟市场的鸿沟将会逐步填平。

以突破性的技术思路:紧耦合+松耦合,实现“可望不可及”的DSA

11月11日,中国集成电路设计业2023年会( ICCAD 2023)在广州保利世贸博览馆举行。在大会上,隼瞻科技 CEO 曾轶做了题为“跨越鸿沟 —— 关于 RISC-V 专用处理器和 DSA 方法学思考”的分享。

在分享中,曾轶详细介绍了隼瞻科技“三位一体”的解决方案,以及如何通过新的技术思路,借助 RISC-V 实现半导体行业探讨多年的 DSA 愿景。

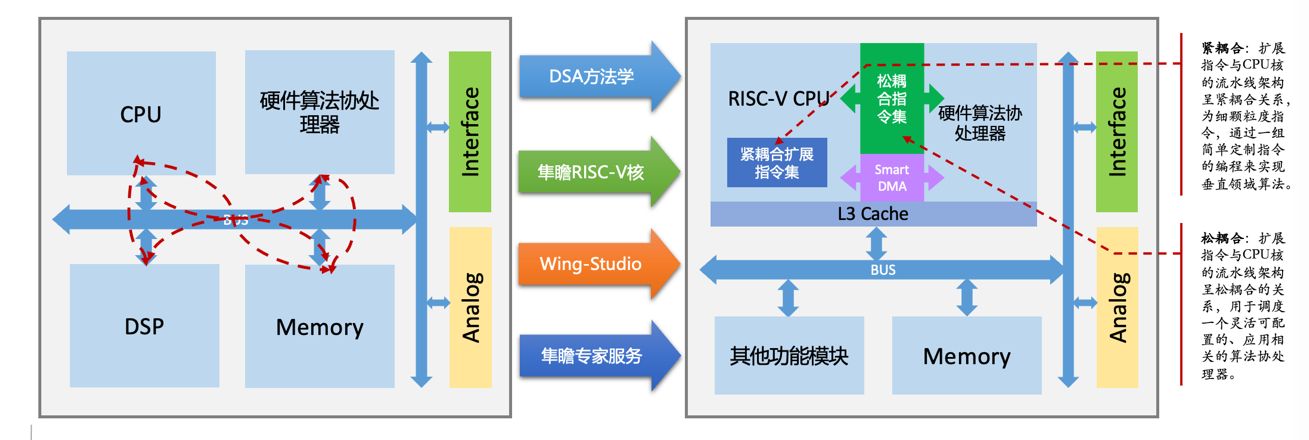

传统的 SOC 架构下,CPU 充当调度核心,算法由硬件协处理器和 DSP 执行,数据通过常规总线在 CPU,协处理器和内存之间传送。近年来随着 AI 等技术发展,数据交互越来越巨量和复杂,导致系统总线越发拥塞,出现了明显的“存算墙”。同时,硬件协处理器在芯片定型生产后难以编程,影响后期市场的灵活性,虽然增加 DSP 能满足后期算法编程需求,但一来授权费用高,二来又增加芯片面积和功耗,整体算力利用率不高。

隼瞻科技运用 DSA 方法论,对算法系统进行了分析与划分:对于使用频率和性能要求高的算法,采用“松耦合”指令集和“Smart DMA”高速总线进行更灵活的硬件算法协处理器调度;对于后期需要灵活编程的算法部分,采用“紧耦合”指令集进行细颗粒度的实现。配合革命性的私有高速缓存池和私有总线,新的芯片架构突破了传统 SOC 架构的极限,克服了“存算墙”的问题,并做到兼顾芯片 PPA 和后期可编程性的平衡。

新技术思路充分利用了 RISC-V 开源架构最大的竞争优势:处理器指令集的灵活性和自主性;同时,也得益于隼瞻科技 ASIP 敏捷开发 EDA 平台 Wing-Studio的协助,高效地完成了以往需要耗费巨量人力物力的“算法芯片化”架构探索。这项技术的成功,让芯片行业曾经可望不可及的 DSA 得以实现。

在分享中,曾轶还向同行展示了隼瞻科技最新的代码密度增强技术,通过最新研发的 RISC-V 代码密度增强指令集,能极大减小程序代码空间,进而有效缩小程序存储器容量,大大节省芯片成本。在此基础上,运用 Wing-Studio平台针对客户具体代码进行分析和优化,还能进一步提升代码密度,目前已经非常逼近 ARM 指令集的密度水平。

ICCAD 2023 刚结束,隼瞻科技又马不停蹄地推出了基于 RISC-V 处理器的 SOC 芯片定制平台“Wing-Ticket”、中断实时性增强技术等新产品和新技术。在国际地缘竞争的大背景下,中国的芯片行业正面临着前所未有的挑战和机遇,RISC-V 作为重要推动力量,必将发挥越来越重要的作用。隼瞻科技将继续“脚踏实地、仰望星空”,全力推动 RISC-V 生态走向成熟商用市场,为中国芯片行业的未来带来更多可能性。

专业名词解释

DSA(Domain-Specific Architecture):客制化的专用领域架构,是一种可编程计算机体系结构,为了在特定的专用领域内能非常有效地运行而定制。与其相反的则是通用架构(例如 CPU)。

ASIP(Application-Specific Instruction-set Processor):面向应用的定制指令集处理器,其指令集是针对特定的应用而设计的。借助这样的设计方式,它具有通用型 CPU 的灵活性和ASIC 的性能。专用指令集处理器的指令集,可通过电路设计软件进行配置。

紧耦合:指扩展指令与 CPU 核的流水线架构呈紧耦合关系,为细颗粒度指令,通过一组简单定制指令的编程来实现垂直领域算法。

松耦合:指扩展指令与 CPU 核的流水线架构呈松耦合关系,用于调度一个灵活可配置的、应用相关的算法协处理器。